Vortex Homepage

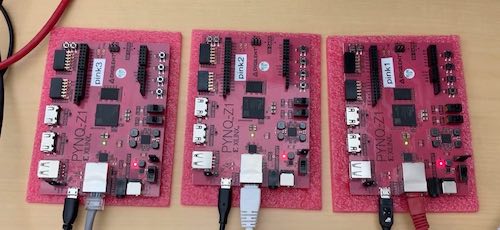

Vortex is an open source Hardware and Software project to support GPGPU based on RISC-V ISA extensions. Currently, Vortex supports OpenCL and it runs on FPGA. The vortex platform is highly customizable and scalable with a complete open source compiler, driver and runtime software stack to enable research in GPU architectures.

Students: Blaise Tine, Roubing Han

Sponsors: Oak Ridge National Lab, Silicon arts

SARAV Website: hparch/undergraduate_research/

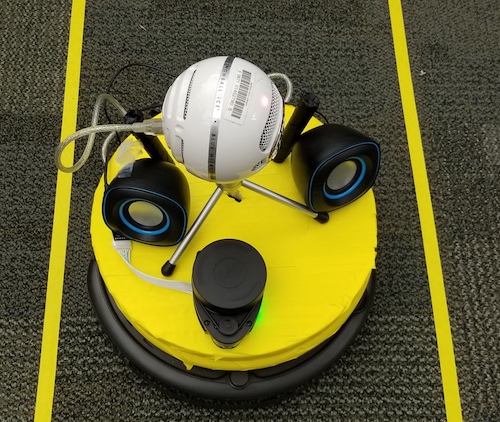

SARAV is an undergraduate oriented research group that focuses on systems and architecture for robotics and autonomous vehicles. The group members are mainly from Georgia Tech undergraduate students and advised by Ramyad Hadidi (PhD candidate), Jiashen Cao (MS student) and Prof. Hyesoon Kim.

Students: Ramyad Hadidi, Jiashen Cao

Drone Build Guide

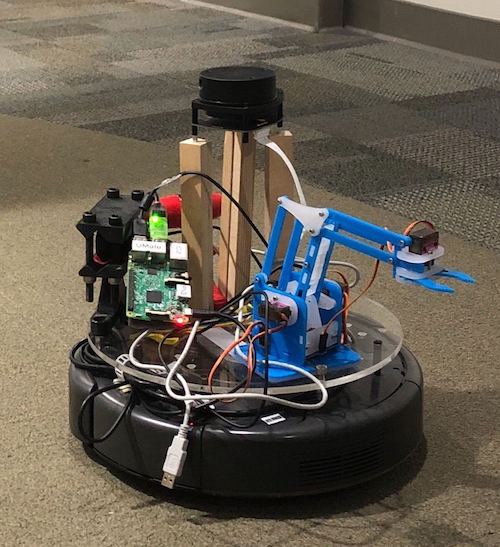

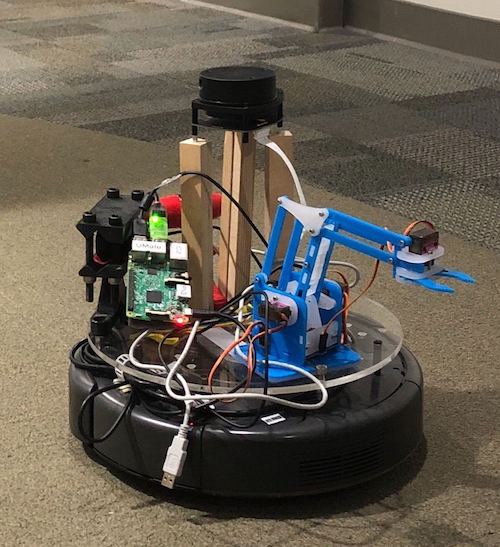

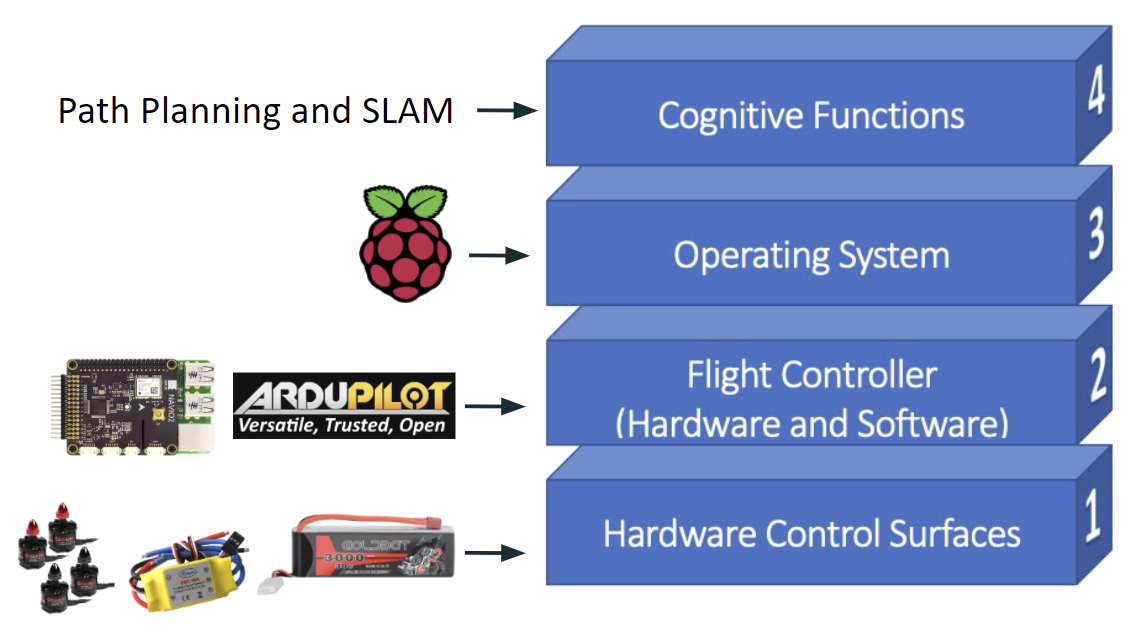

Over the last decade, significant progress has been made in developing autonomous drones, with countless applications such as aerial mapping, natural disaster recovery, search and rescue, ecology, and entertainment. Thus, many control, planning, and perception methods have been assimilated for drones. Nevertheless, drones must operate under quite different conditions than any other compute-based agent. First, weight and power are restrictive parameters in drones. Second, drones must arbitrate between their limited compute, energy, and electromechanical resources not only based on the current tasks and local conditions eg: wind, but also according to the flight plan. Despite huge technological advances, these problems have been approached in isolation, and the end-to-end system design-space tradeoffs are largely unknown. In this project, we quantify and analyze and quantify different drone parameters and their subsystems.

Students: Ramyad Hadidi, Sam Jijina

The goal of this project is to provide architectural innovations and mechanisms for increasing the performance of GPGPU applications. The initial focus has been on improving tolerance (or reducing) to memory access latency and on studying the effect of instruction fetch and DRAM scheduling on the performance of GPGPU applications. For improving tolerance to memory accesses, we have proposed both software and hardware based prefetcher mechanisms for GPUs with adaptive behavior. We are also working on optimized memory controllers for further improving tolerance to memory accesses.

Students: Hyojong Kim, Dilan Manatunga

Sponsors: Intel, Sandia National Lab

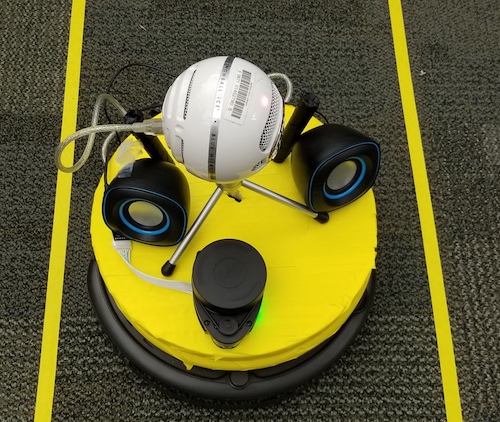

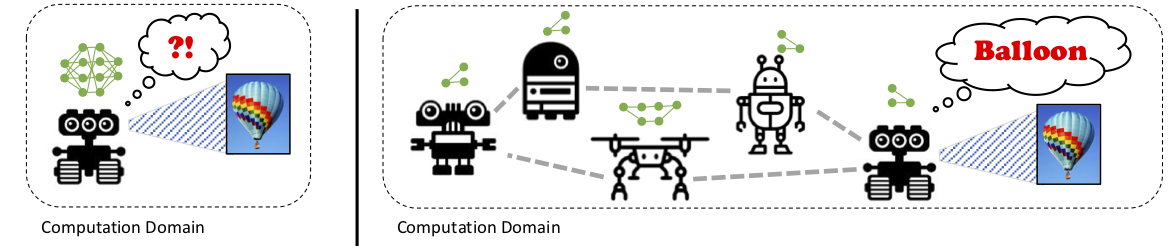

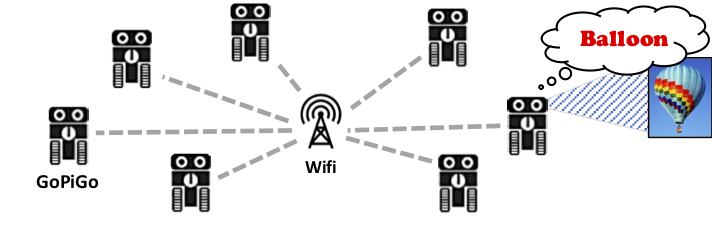

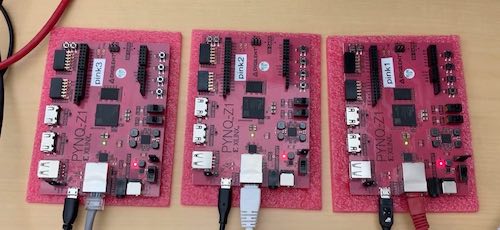

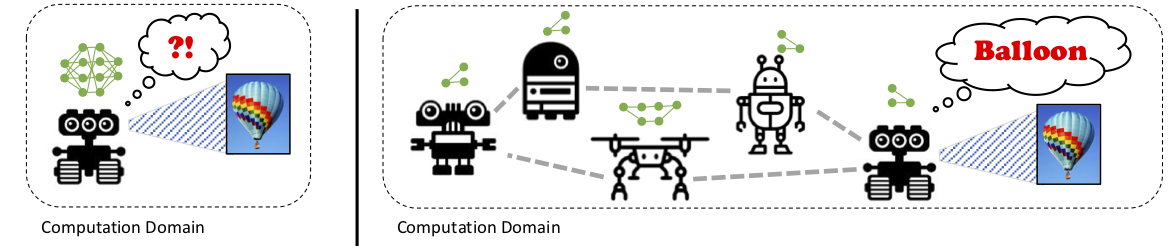

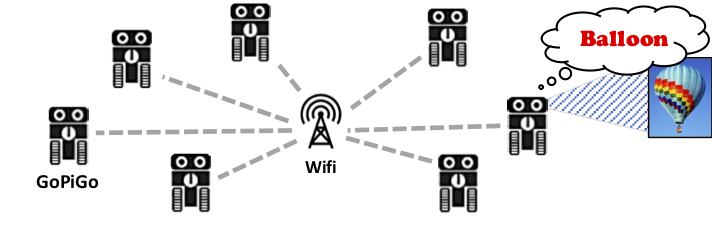

Recognition ability and, more broadly, machine learning techniques enable robots and IoT devices to perform complex tasks and allow them to function in diverse situations. In fact, these devices can easily access an abundance of sensor data that are recorded in real time such as speech, image, and video. Since such data are time sensitive, processing them in real time is a necessity. Furthermore, usually recoreded data are highly sensitive and requires careful privacy constarints. At the same time, machine learning techniques are known to be computationally intensive and resource hungry. As a result, an individual resource-constrained robot or IoT device, in terms of computation power and energy supply, is often unable to handle such heavy real-time computations alone. To overcome this obstacle, in this project, we are working on techniques and frameworks to harvest the aggregated computational power of several devices to perform real-time perception.

Students: Ramyad Hadidi, Jiashen Cao

Sponsors: Intel, NSF

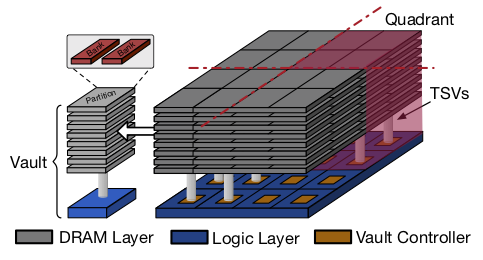

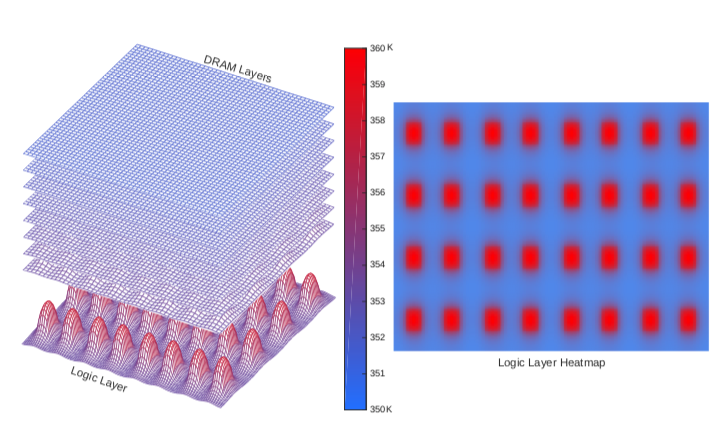

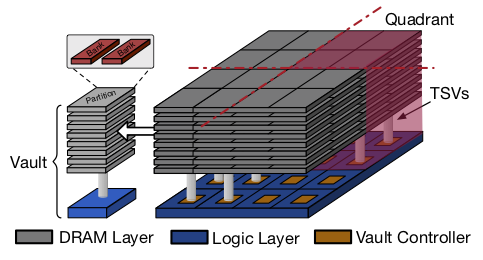

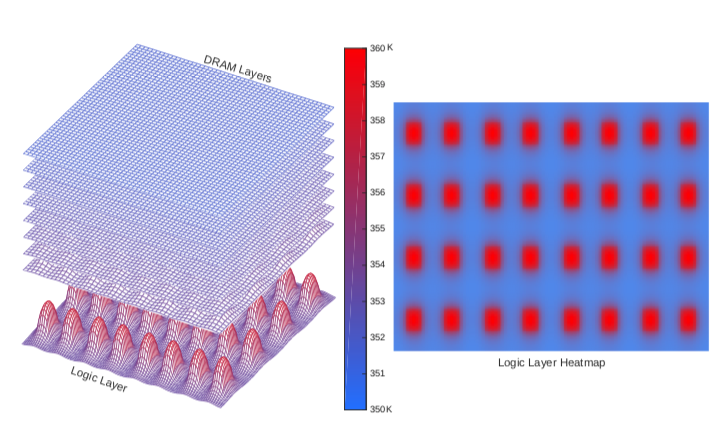

Three-dimensional (3D)-stacking technology, which enables the integration of DRAM and logic dies, offers high bandwidth and low energy consumption. This technology also empowers new memory designs for executing tasks not traditionally associated with memories. A practical 3D-stacked memory is Hybrid Memory Cube (HMC), which provides significant access bandwidth and low power consumption in a small area. In this project, we characterize and analyze the behaviors of 3D-stacked memories such as HMC, and provide novel techniques and methods to execute current applications on these devices more efficiently.

Students: Euna Kim, Bahar Asgari

Sponsors: NSF, LPs

Memory safety violations, caused by illegal use of pointers in unsafe programming languages such as C and C++, have been a major threat to modern computer systems. While numerous software solutions have been proposed, their high performance overhead limits their usage to testing and debugging. In this project, we study the challenges of existing memory safety solutions and develop a low-overhead yet secure runtime solution achieved with novel micro-architectural supports.

Students: Yonghae Kim, Jaewon Lee